In essence, what this project is aimed at doing is make the build logic code easier to reason about and follow, which in turn would make it easier to separate it from our resolution logic and make life easier when we do go ahead with the new resolution logic - #6536 is for figuring out the communication and overall approach for that.Īnother thing I'll note is that, this was the main blocker/issue/tricky-thing-that-I-sunk-time-into when I was working on a weekend-prototype ( ). This, however, also means that we need to make it easier to actually modify the resolution and build logic, which have been entangled in the codebase since I started working on pip.

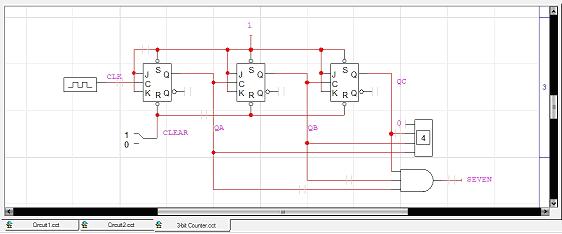

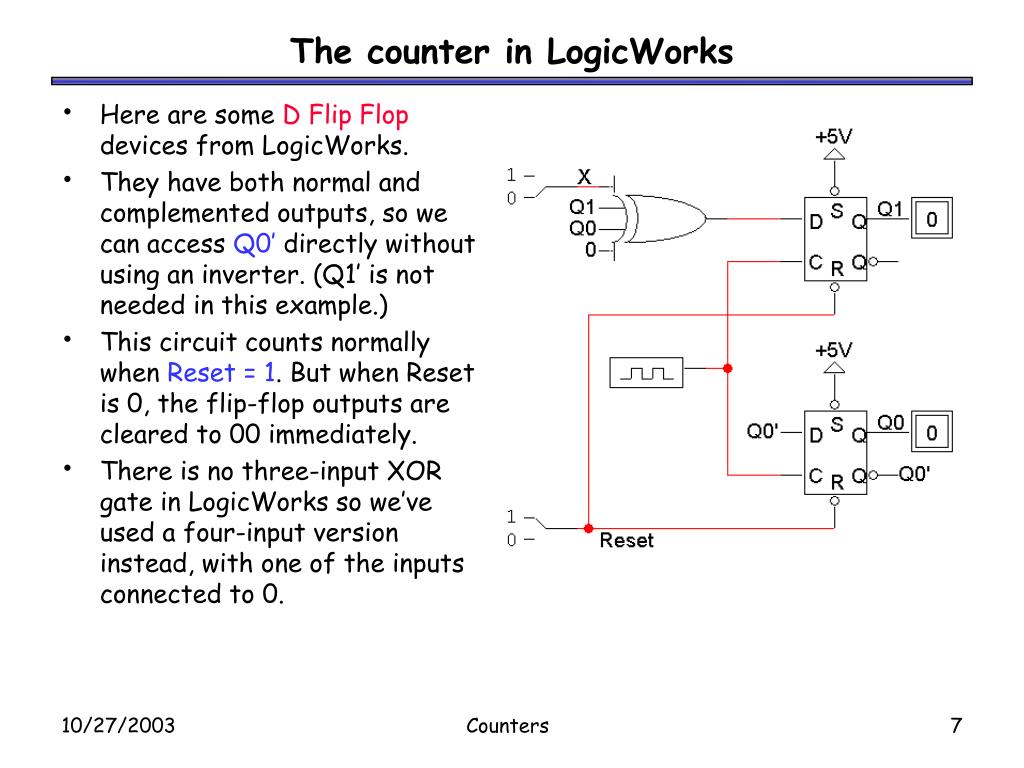

operate on a more "abstract" space, like the resolvelib/zazo abstractions). Ideally, the resolver should not see that this is happening (i.e. We have to perform the fetch-build-query during our resolution process. I think this project, is closely related to the actually implementing the resolver. Observe it for yourself.I notice that my previous response is super terse, so I'll elaborate a bit.Lowest pin, by F, is lower order bit 0.Enter 4 bits in hex - useful for our 4 bit bus.Sometimes just need to toggle inputs University of Illinois at Urbana Champaign.C: conflict value - 2 conflicting pins with same label.Z: unknown value - somewhere a pin is disconnected.To move switches (and most of the other components too) hold down shift while clicking.Don't use five AND-2 gates! University of Illinois at Urbana Champaign.Use AND-3 plus AND-4 - How to connect?.Use AND-8 - What to do with remaining pins?.Use some logic BUT be careful on the implications.Entire wire & pins should turn yellow when selected University of Illinois at Urbana Champaign.Ends must contact - intersect is not enough!.Name: to connect pins without drawing a wire University of Illinois at Urbana Champaign.Name: useful to label components in big circuits.Arrows make gate point left, right, up, or down.Show background grid University of Illinois at Urbana Champaign.Show printed page breaksMake sure components don't span page breaks.Type: Symbol libraries (to be used later) University of Illinois at Urbana Champaign.University of Illinois at Urbana Champaign Easier to verify that everything happened correctly. As alternative to using a fixed clock speed, use binary switch as "clock" and manually toggle when a clock cycle happens.Bus wire (multi-bit) University of Illinois at Urbana Champaign.

Zap to delete lines & components - useful to cleanup mistakes.Zoom in and out using toolbar University of Illinois at Urbana Champaign.Can be accessed underView Timing Window.single click in layout to place device University of Illinois at Urbana Champaign.Simulation Logic: adder, clock, flip-flop, decoder, mux.Simulation IO: binary switch, hex keyboard, binary probe, hex display.Debugging University of Illinois at Urbana Champaign.Typically, data flows from left to right.(Except in our datapath, where it flowsup down up) University of Illinois at Urbana Champaign.Use labels on pins, instead of crossing wires everywhere.Even if you are working in groups on the MPs (not HWs), use it for some time.Time University of Illinois at Urbana Champaign.A software that allows simulation of hardware components and their interactions.Check the website for office hours?(no changes, but still…) University of Illinois at Urbana Champaign.Using LogicWorks Celal Ziftci CS 231 – Fall 2005 University of Illinois at Urbana Champaign

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed